UNIVERSITE Joseph FOURIER, Grenoble U.F.R. d' Informatique et Maths. Appliquées

Licence Sciences et Technologie Parcours MIN, INF, IAG, BIN UE INF241

# Introduction aux Architectures Logicielles et Matérielles

Notes de COURS - 2008/2009

# Table des matières

| 1 | Coc | dage de                                    | es informations et représentation des naturels par des vecteurs binaires | 6         |  |  |  |  |  |  |  |

|---|-----|--------------------------------------------|--------------------------------------------------------------------------|-----------|--|--|--|--|--|--|--|

|   | 1.1 | Codag                                      | e                                                                        | 6         |  |  |  |  |  |  |  |

|   | 1.2 | Codag                                      | e d'ensemble structuré d'informations                                    | 7         |  |  |  |  |  |  |  |

|   | 1.3 | Représ                                     | sentation des naturels par des vecteurs binaires                         | 9         |  |  |  |  |  |  |  |

|   | 1.4 | 4 Ecriture en base 16 ou base hexadécimale |                                                                          |           |  |  |  |  |  |  |  |

|   | 1.5 | Représ                                     | sentation des relatifs par des vecteurs binaires                         | 10        |  |  |  |  |  |  |  |

|   |     | 1.5.1                                      | une première idée : signe et valeur absolue                              | 10        |  |  |  |  |  |  |  |

|   |     | 1.5.2                                      | complément à deux                                                        | 10        |  |  |  |  |  |  |  |

|   | 1.6 | Opérat                                     | tions                                                                    | 11        |  |  |  |  |  |  |  |

|   |     | 1.6.1                                      | Addition                                                                 | 11        |  |  |  |  |  |  |  |

| 2 | Mo  | dèle de                                    | e Von Neumann : Qu'est ce qu'un ordinateur                               | <b>12</b> |  |  |  |  |  |  |  |

|   | 2.1 | Mémoi                                      | ire (sous-entendu centrale)                                              | 12        |  |  |  |  |  |  |  |

|   |     | 2.1.1                                      | Définition                                                               | 12        |  |  |  |  |  |  |  |

|   |     | 2.1.2                                      | Actions sur la mémoire                                                   | 14        |  |  |  |  |  |  |  |

|   |     | 2.1.3                                      | Différents types; vision très concrète                                   | 15        |  |  |  |  |  |  |  |

|   | 2.2 | Entrée                                     | es sorties                                                               | 15        |  |  |  |  |  |  |  |

|   | 2.3 | Proces                                     | seur                                                                     | 16        |  |  |  |  |  |  |  |

|   |     | 2.3.1                                      | Actions, processeur/mémoire                                              | 16        |  |  |  |  |  |  |  |

|   |     | 2.3.2                                      | Composition du processeur                                                | 16        |  |  |  |  |  |  |  |

|   |     | 2.3.3                                      | Notion d'exécution séquentielle des instructions                         | 16        |  |  |  |  |  |  |  |

|   |     | 2.3.4                                      | Notion élémentaire de langage machine : première définition              | 17        |  |  |  |  |  |  |  |

|   |     | 2.3.5                                      | C'est quoi les processeurs?                                              | 17        |  |  |  |  |  |  |  |

| 3 | Lan | igage d                                    | 'assemblage, langage machine                                             | 18        |  |  |  |  |  |  |  |

|   | 3.1 | Vie d'u                                    | un programme                                                             | 18        |  |  |  |  |  |  |  |

|   | 3.2 | Langag                                     | ge machine                                                               | 19        |  |  |  |  |  |  |  |

|   | 3.3 | Instruc                                    | ctions et programmes en langage machine                                  | 19        |  |  |  |  |  |  |  |

|   |     | 3.3.1                                      | Instructions de calcul (ou d'échanges de place) entre des informations   |           |  |  |  |  |  |  |  |

|   |     |                                            | mémorisées                                                               | 20        |  |  |  |  |  |  |  |

|   |     | 3.3.2                                      | Instructions de rupture de séquence                                      | 20        |  |  |  |  |  |  |  |

|   |     | 3.3.3                                      | Remarques:                                                               | 20        |  |  |  |  |  |  |  |

|   | 3.4 | Langag                                     | ge d'assemblage                                                          | 21        |  |  |  |  |  |  |  |

|   |     | 3.4.1                                      | Langage textuel, notation des instructions                               | 21        |  |  |  |  |  |  |  |

|   |     | 3.4.2                                      | Désignation des objets                                                   | 21        |  |  |  |  |  |  |  |

|   |     | 3.4.3                                      | Séparation données instructions                                          | 22        |  |  |  |  |  |  |  |

|   |     | 3.4.4                                      | Etiquettes                                                               | 23        |  |  |  |  |  |  |  |

| 4 | Inst                 | tructions de rupture de séquence et Programmation des structures de contrôle     | 24 |

|---|----------------------|----------------------------------------------------------------------------------|----|

|   | 4.1                  | Exécution séquentielle et ruptures de séquences                                  | 24 |

|   |                      | 4.1.1 Exécution séquentielle et ruptures de séquences                            | 24 |

|   | 4.2                  | Conditionnelles                                                                  | 26 |

|   |                      | 4.2.1 Version Paul                                                               | 26 |

|   |                      | 4.2.2 Version Fabienne                                                           | 27 |

|   | 4.3                  | boucles                                                                          | 28 |

|   |                      | $4.3.1$ I1; while ExpCond do {I2; I3}; I4                                        | 28 |

|   |                      |                                                                                  | 29 |

|   |                      |                                                                                  | 29 |

|   | 4.4                  | ,                                                                                | 29 |

|   |                      |                                                                                  | 29 |

|   |                      |                                                                                  | 30 |

|   | 4.5                  | ·                                                                                | 30 |

|   | 4.6                  |                                                                                  | 31 |

|   | 1.0                  | <u> </u>                                                                         | -  |

| 5 | $\operatorname{Pro}$ | grammation à partir des automates reconnaisseurs                                 | 32 |

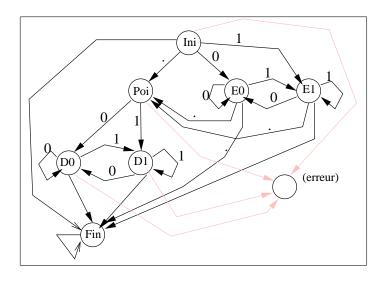

|   | 5.1                  | Automate avec actions à nombre fini d'états : Définition commentée               | 32 |

|   | 5.2                  | Exemple                                                                          | 33 |

|   |                      | 5.2.1 Evaluation                                                                 | 33 |

|   |                      | 5.2.2 Modélisation de l'évaluation par un Automate d'état fini avec actions      | 33 |

|   | 5.3                  | Mise en œuvre logicielle                                                         | 34 |

|   |                      | 5.3.1 Idée de la mise en œuvre par un langage évolué                             | 34 |

|   |                      |                                                                                  | 34 |

|   |                      |                                                                                  | 35 |

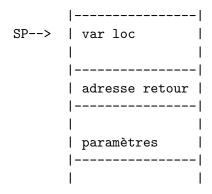

| 6 | Pro                  | ogrammation des appels de procédure et fonction (3 Séances)                      | 43 |

| Ü | 6.1                  |                                                                                  | 43 |

|   | 6.2                  | ·                                                                                | 43 |

|   | 0.2                  | 6.2.1 Traduction langage d'assemblage ARM en plaçant toutes les valeurs dans des | 10 |

|   |                      | • • • •                                                                          | 44 |

|   |                      |                                                                                  | 45 |

|   |                      |                                                                                  | 46 |

|   |                      |                                                                                  | 46 |

|   |                      |                                                                                  | 46 |

|   | 6.3                  |                                                                                  | 47 |

|   | 0.0                  | **                                                                               | 47 |

|   |                      |                                                                                  | 48 |

|   |                      | •                                                                                | 48 |

|   |                      | 11                                                                               | 50 |

|   | 6.4                  |                                                                                  | 50 |

|   | 6.4                  | *                                                                                |    |

|   |                      |                                                                                  | 51 |

|   |                      | **                                                                               | 54 |

|   | c r                  | *                                                                                | 59 |

|   | 6.5                  |                                                                                  | 60 |

|   |                      | ·                                                                                | 60 |

|   |                      | 6.5.2 Programmation en langage d'assemblage                                      | 61 |

| 1 | inti | roduction a la structure interne des processeurs : une machine a 5 instructions       | 63 |

|---|------|---------------------------------------------------------------------------------------|----|

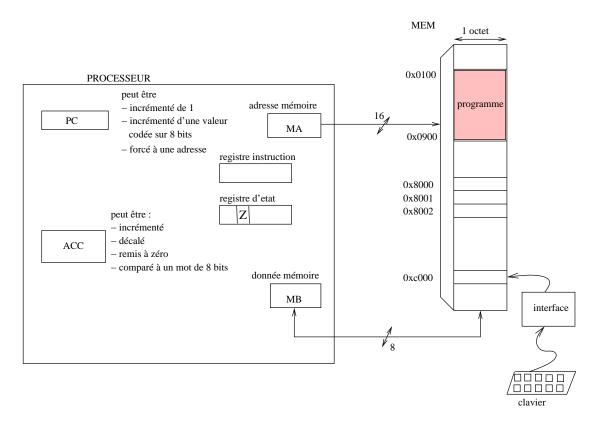

|   | 7.1  | Description du processeur vu du programmeur                                           | 63 |

|   | 7.2  | Un exemple de programme                                                               | 63 |

|   | 7.3  | Description de l'exécution du programme = interprétation des différentes instructions | 64 |

|   |      | 7.3.1 Interpréter l'exemple                                                           | 64 |

|   |      | 7.3.2 Vision algorithmique de cette interprétation                                    | 64 |

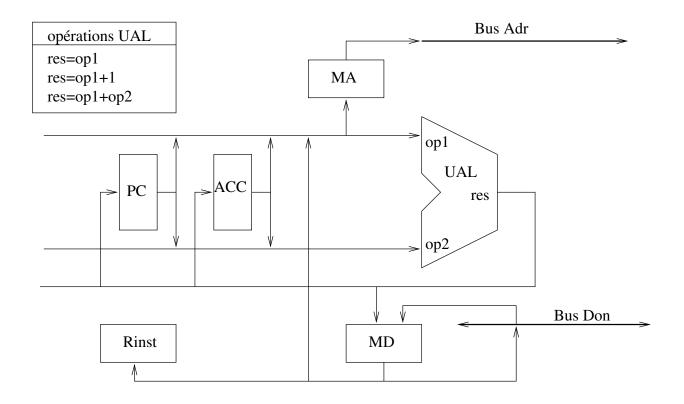

|   | 7.4  | Organisation du processeur                                                            | 65 |

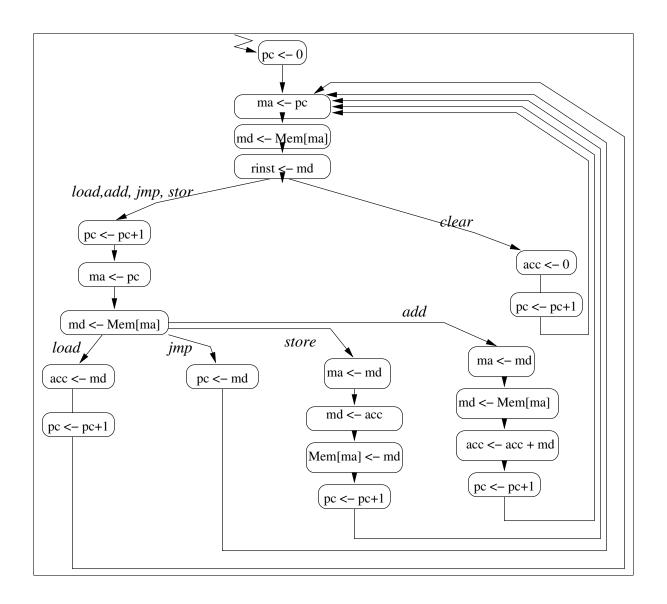

|   | 7.5  | Automate d'interprétation des instructions du processeur                              | 66 |

|   |      | 7.5.1 Une première version                                                            | 66 |

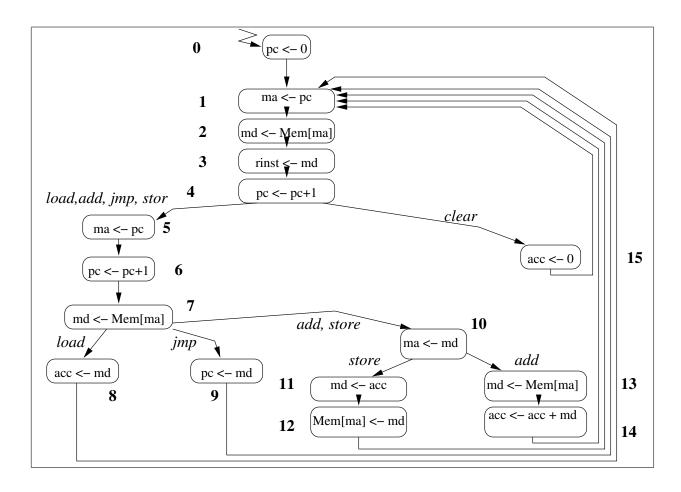

|   |      | 7.5.2 Version améliorée                                                               | 66 |

|   | 7.6  | Déroulement d'un programme, au cycle près                                             | 66 |

|   |      |                                                                                       |    |

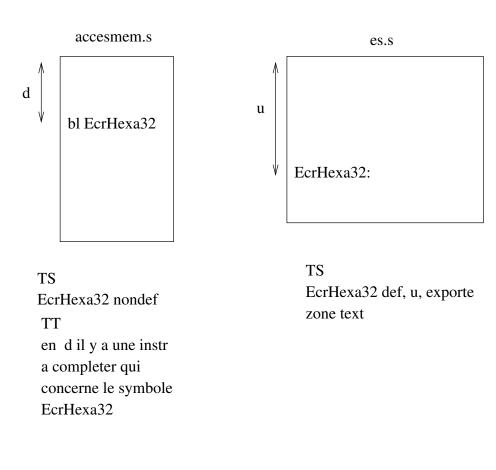

| 8 | Vie  | des programmes                                                                        | 71 |

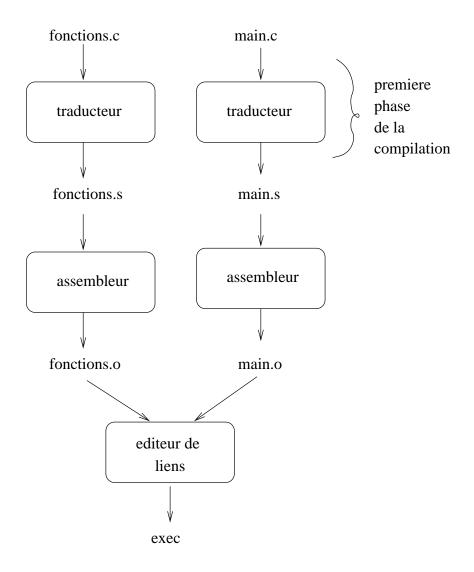

|   | 8.1  | Etapes permettant de produire un exécutable                                           | 71 |

|   |      | 8.1.1 Un exemple en langage C                                                         | 71 |

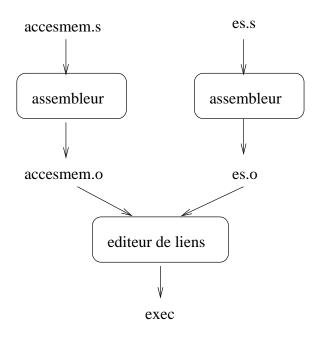

|   |      | 8.1.2 Un exemple en langage d'assemblage                                              | 72 |

|   | 8.2  | Traduction du langage C en langage d'assemblage                                       | 74 |

|   | 8.3  | Assembleur                                                                            | 74 |

|   |      | 8.3.1 Que contient un fichier .s?                                                     | 74 |

|   |      | 8.3.2 Que contient un fichier .o?                                                     | 75 |

|   |      | 8.3.3 Etapes d'un assembleur                                                          | 75 |

|   | 8.4  | Editeur de liens                                                                      | 75 |

|   | 8.5  | Jusqu'où aller?????                                                                   | 77 |

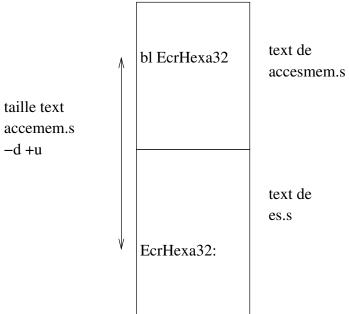

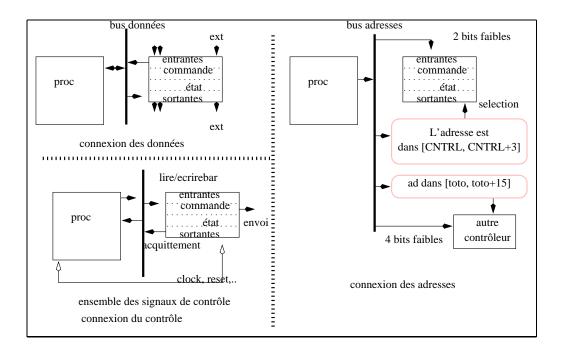

| 9 | Org  | ganisation d'un ordinateur                                                            | 78 |

#### Introduction

Nous allons étudier comment les PROGAMMES sont exécutés par un PROCESSEUR.

Du point de vue physique un processeur est un ensemble de circuits, un circuit étant un assemblage de transistors. Un transistor est un dispositif électronique fonctionnant comme un interrupteur (mais actif : il pompe de l'énergie sur l'alim du circuit, il a besoin d'être alimenté et il produit de l'énergie, suffisamment pour faire basculer l'interrupteur suivant ...)

Nous étudierons plusieurs types de processeurs, comme on étudie, parfois en informatique, des algorithmes. En TP nous travaillerons avec un processeur appelé ARM. On le trouve entre autres dans des téléphones portables, des consoles de jeu.

On ne va pas parler dans ce cours de la conception des circuits (cours ALM en L3). On va se préoccuper du fonctionnement logique d'un processeur.

Quand on parle de processeur, on parle de *circuit intégré* (sur un même support) de *traitement numérique de l'information* (les informations sont représentées par des nombres).

Rem : plusieurs types de représentation de l'information :

- représentation d'une tension électrique sur le cadran d'un voltmètre, info rep. par la position de l'aiguille : représentation analogique

- représentation de la tension par une valeur entière : représentation numérique, on dit aussi digitale.

#### Bibliographie:

- Architectures logicielles et matérielles, Amblard, Fernandez, Lagnier, Maraninchi, Sicard, Waille,

Dunod 2000 et web (TIMA editions)

- Architecture des ordinateurs, Cazes, Delacroix, Dunod 2003

## Chapitre 1

# Codage des informations et représentation des naturels par des vecteurs binaires

#### 1.1 Codage

Un codage est une correspondance un-à-un (bijection) entre un ensemble d'informations et un ensemble de naturels. Le plus souvent, pour N informations, on choisit l'intervalle [0, N-1]. Fonction de codage dans un sens, de décodage dans l'autre. La fonction de codage a un nom car on peut inventer plusieurs fonctions.

Exemples On donne ces codes sur papier aux étudiants plutôt que de les faire copier au tableau!!

Ex1: Codage des couleurs du Commodore 64

propriétés intéressantes : pas d'ordre apparent, pas de structure clair/foncé,...

| В | $b_3b_2b_1b_0$ |        | В | $b_3b_2b_1b_0$  |        | В  | $b_3b_2b_1b_0$ |            |

|---|----------------|--------|---|-----------------|--------|----|----------------|------------|

| 0 | 0 0 0 0        | noir   | 5 | 0 1 0 1         | vert   | 10 | 1010           | rose       |

| 1 | 0 0 0 1        | blanc  | 6 | 0110            | bleu   | 11 | $1\ 0\ 1\ 1$   | gris foncé |

| 2 | 0 0 1 0        | rouge  | 7 | 0 1 1 1         | jaune  | 12 | $1\ 1\ 0\ 0$   | gris moyen |

| 3 | 0 0 1 1        | cyan   | 8 | $1 \ 0 \ 0 \ 0$ | orange | 13 | $1\ 1\ 0\ 1$   | vert pâle  |

| 4 | 0 1 0 0        | violet | 9 | $1\ 0\ 0\ 1$    | brun   | 14 | $1\ 1\ 1\ 0$   | bleu pâle  |

|   |                |        |   |                 |        | 15 | 1111           | gris pâle  |

$Code_{-}C64 \text{ (violet)} = 4$ ;  $Decode_{-}C64 \text{ (12)} = gris moyen.$

Ex2: Codage des 16 couleurs sur les premiers PC couleurs

En regardant le code en base 2, on voit un bit de rouge (b2), un bit de vert (b1), un bit de bleu (b0) et un bit de clair (b3). Le codage du violet est fait de bleu et de rouge...

| В | $b_3b_2b_1b_0$ |       | В | $b_3b_2b_1b_0$ |           | В  | $b_3b_2b_1b_0$ |           |

|---|----------------|-------|---|----------------|-----------|----|----------------|-----------|

| 0 | 0 0 0 0        | noir  | 5 | 0 1 0 1        | violet    | 10 | 1010           | vert pâle |

| 1 | 0001           | bleu  | 6 | $0\ 1\ 1\ 0$   | brun      | 11 | 1011           | cobalt    |

| 2 | 0010           | vert  | 7 | $0\ 1\ 1\ 1$   | gris      | 12 | 1100           | rose      |

| 3 | 0011           | cyan  | 8 | $1\ 0\ 0\ 0$   | noir pâle | 13 | $1\ 1\ 0\ 1$   | mauve     |

| 4 | 0100           | rouge | 9 | $1\ 0\ 0\ 1$   | bleu pâle | 14 | 1110           | jaune     |

|   |                |       |   |                |           | 15 | 1111           | blanc     |

Ex3: L'ensemble des caractères affichables

code ASCII: "American Standard Code for Information Interchange"

| 32  | Ш            | 33  | !            | 34  | "            | 35  | #            | 36  | \$           | 37  | %            | 38  | &            | 39  | ,   |

|-----|--------------|-----|--------------|-----|--------------|-----|--------------|-----|--------------|-----|--------------|-----|--------------|-----|-----|

| 40  | (            | 41  | )            | 42  | *            | 43  | +            | 44  | ,            | 45  | -            | 46  |              | 47  | /   |

| 48  | 0            | 49  | 1            | 50  | 2            | 51  | 3            | 52  | 4            | 53  | 5            | 54  | 6            | 55  | 7   |

| 56  | 8            | 57  | 9            | 58  | :            | 59  | ;            | 60  | <            | 61  | =            | 62  | >            | 63  | ?   |

| 64  | @            | 65  | A            | 66  | В            | 67  | $\mathbf{C}$ | 68  | D            | 69  | $\mathbf{E}$ | 70  | $\mathbf{F}$ | 71  | G   |

| 72  | Η            | 73  | I            | 74  | J            | 75  | $\mathbf{K}$ | 76  | L            | 77  | Μ            | 78  | N            | 79  | О   |

| 80  | Р            | 81  | Q            | 82  | $\mathbf{R}$ | 83  | $\mathbf{S}$ | 84  | Τ            | 85  | U            | 86  | V            | 87  | W   |

| 88  | X            | 89  | Y            | 90  | $\mathbf{Z}$ | 91  | [            | 92  | \            | 93  | ]            | 94  | ^            | 95  | _   |

| 96  | 6            | 97  | $\mathbf{a}$ | 98  | b            | 99  | $\mathbf{c}$ | 100 | d            | 101 | e            | 102 | f            | 103 | g   |

| 104 | h            | 105 | i            | 106 | j            | 107 | k            | 108 | 1            | 109 | m            | 110 | n            | 111 | О   |

| 112 | p            | 113 | $\mathbf{q}$ | 114 | $\mathbf{r}$ | 115 | $\mathbf{s}$ | 116 | $\mathbf{t}$ | 117 | u            | 118 | $\mathbf{v}$ | 119 | w   |

| 120 | $\mathbf{x}$ | 121 | У            | 122 | $\mathbf{Z}$ | 123 | {            | 124 |              | 125 | }            | 126 | ~            | 127 | del |

Code\_ascii (q) = 113; Decode\_ascii (51) = 3 .... chiffre nombre...

On obtient ce tableau par la commande Unix man ascii.

Propriétés : ordre, passage min/maj.

#### 1.2 Codage d'ensemble structuré d'informations

Ensemble ordonné ↔ intervalle de naturels en respectant l'ordre (ex : lettres de l'aphabet).

Ensemble muni de **relations et d'opérations** : codage qui "respecte" les relations et opérations. (Exemple ordre alphabétique dans ASCII, majuscule + 32 = minuscule).

Ensemble **produit cartésien** : codage par des n\_uplets (positions sur terre, lattitude, longitude ; ensemble des jours de l'année et jour de la semaine, numéro de semaine sur les tickets de stationnement).

Ensemble "hiérarchisé" d'éléments "regroupables" (critères à discuter) exemple villes olympiques. (généralisation : feuilles d'un arbre)

#### Ex4: Code des villes olympiques

Soit l'ensemble suivant de villes Olympiques. E= {Albertville, Athènes, Atlanta, Chamonix, Grenoble, Los Angeles, Melbourne, Mexico, Montréal, Paris, Pékin, Rome, Sydney, Tokyo}

Ce sont les feuilles d'un arbre où la hiérarchie est donnée :

- par les continents (niveau 1) Amérique : 0; Asie : 1; Europe : 2.

- par les pays (niveau 2) en Amérique : Canada : 0; E.U. 1; Mexique : 2

- par les régions (niveau 3) en France : Ile de France : 0; Rhône-Alpes : 1

On code chaque continent, pays, région, ville par un entier, le code d'une ville est alors un quadruplet. Pour les objets de même niveau, on utilise l'ordre alphabétique.

| continent | pays       | région          | ville       | code quadruplet |

|-----------|------------|-----------------|-------------|-----------------|

| Amérique  | Canada     |                 | Montréal    | (0, 0, 0, 0)    |

|           | Etats-Unis | Californie      | Los Angeles | (0, 1, 0, 0)    |

|           |            | Géorgie         | Atlanta     | (0, 1, 1, 0)    |

|           | Mexique    |                 | Mexico      | (0, 2, 0, 0)    |

| Asie      | Chine      |                 | Pékin       | (1, 0, 0, 0)    |

|           | Japon      |                 | Tokyo       | (1, 1, 0, 0)    |

| Europe    | France     | Ile de France   | Paris       | (2, 0, 0, 0)    |

|           |            | Rhône-Alpes     | Albertville | (2, 0, 1, 0)    |

|           |            |                 | Chamonix    | (2, 0, 1, 1)    |

|           |            |                 | Grenoble    | (2, 0, 1, 2)    |

|           | Grece      |                 | Athenes     | (2, 1, 0, 0)    |

|           | Italie     |                 | Rome        | (2, 2, 0, 0)    |

| Océanie   | Australie  | New South Wales | Sydney      | (3, 0, 0, 0)    |

|           |            | Victoria        | Melbourne   | (3, 0, 1, 0)    |

| a         |            |                 | , '         |                 |

Si ce code vous parait "inventé", essayez donc de comprendre le code des Unités d'enseignement du DSU, il y a quelques ressemblances...

Codage d'instructions, de commandes, d'ordres,... On peut imaginer des codes par de tels N-iplets pour des ordres, des commandes à un robot, des instructions d'ordinateur,...

| numéro du bras         | direction |  | angle    | vitesse de déplacement |     |  |

|------------------------|-----------|--|----------|------------------------|-----|--|

| 3                      | Nord      |  | 135      | haute                  |     |  |

| 2                      | Sud       |  | 45       | très faible            |     |  |

| numéro de case mémoire |           |  | actic    | n                      |     |  |

| 12345                  |           |  | remise à | zéro                   | ••• |  |

| 47                     |           |  | ncrémen  | tation                 |     |  |

#### Correspondance entre n\_uplet et naturel

**Ex5**: code COUPLE3\_4

$$\{0, 1, 2, 3\} \times \{0, 1, 2, 3, 4\}$$

est codé par  $\{0, 1, 2, ..., 19\}$  il y a 4\*5=20 informations COD\_COUPLE3\_4 (  $(0, 3)$  ) = 0 x 5 + 3 = 3 DECOD\_COUPLE3\_4 (11) = ( 2, 1 ) Compléter le tableau ci-après :

|       | 0     | 1     | 2       | 3       | 4       |

|-------|-------|-------|---------|---------|---------|

| 0     | (0,0) | (0,1) | (0,2)   | (0,3)   | (0,4)   |

|       | 0     | 1     | 2       | 3       | 4       |

| 1     | (1,0) | (1,1) | (1,2)   | (1,3)   | (1,4)   |

|       |       |       |         |         |         |

|       | 5     | 6     | 7       | 8       | 9       |

|       |       |       | 7       | 8       | 9       |

| <br>3 |       |       | 7 (3,2) | 8 (3,3) | 9 (3,4) |

2 formules à savoir : (soit par coeur soit à savoir retrouver vite et sans erreur) COD\_COUPLE3\_4 ( (a, b) ) = a x 5 + b DECOD\_COUPLE3\_4 ( n ) = ( n div 5, n reste 5 )

La simplicité des deux dernières formules justifie le fait que l'on numérote à partir des deux dernières formules justifie le fait que l'on numérote à partir de la simplicité des deux dernières formules justifie le fait que l'on numérote à partir de la simplicité des deux dernières formules justifie le fait que l'on numérote à partir de la simplicité des deux dernières formules justifie le fait que l'on numérote à partir de la simplicité des deux dernières formules justifie le fait que l'on numérote à partir de la simplicité des deux dernières formules justifie le fait que l'on numérote à partir de la simplicité des deux dernières formules justifie le fait que l'on numérote à partir de la simplicité des deux dernières formules justifie le fait que l'on numérote à partir de la simplicité des deux dernières formules justifie le fait que l'on numérote à partir de la simplicité des deux dernières formules justifie le fait que l'on numérote à partir de la simplicité des deux dernières formules justifie le fait que l'on numérote à partir de la simplicité des deux dernières formules justifie le fait que l'on numérote à la simplicité des deux dernières de la simplicité des deux dernières de la simplicité de la simplificité de la simplici

La simplicité des deux dernières formules justifie le fait que l'on numérote à partir de 0 plutôt que de 1.

**Où est le code?** Le code n'est pas dans l'information codée : 14 est le code du jaune dans le code des couleurs du PC (Ex2) et 14 est le code du couple (2,4) dans le code de l'Ex5.

Pour interpréter, comprendre une info codée il fautr connaitre le code. Le code de l'info ne donne rien, c'est le système de traitement de l'info (logiciel ou matériel) qui "connait" le code sinon il ne peut pas la traiter.

#### 1.3 Représentation des naturels par des vecteurs binaires

Avec N chiffres en base b on peut représenter les  $b^N$  naturels de l'intervalle  $[0, b^N-1]$  en numération de position.

Sur X chiffres binaires on peut écrire les  $2^X$  naturels de l'intervalle  $[0,..,2^X-1]$

Ex : en base 10 avec 3 chiffres onn peut rep. les  $10^3$  naturels de l'intervalle [0,999].

**Apprendre par coeur** le tableau des puissances (arrondies!) de 2 et l'ordre de grandeur  $2^{10} \approx 10^3$ .

| X | $2^X$ | $\mid X$ | $2^X$                      | X  | $2^X$                                                    |

|---|-------|----------|----------------------------|----|----------------------------------------------------------|

| 0 | 1     | 4        | 16                         | 20 | $1~048~576~(\approx 1~000~000,~1~{ m M\'ega})$           |

| 1 | 2     | 8        | 256                        | 30 | $1~073~741~824~(\approx 1~000~000~000,~1~\mathrm{Giga})$ |

| 2 | 4     | 10       | $1\ 024\ (\approx 1\ 000)$ | 32 | 4 294 967 296                                            |

| 3 | 8     | 16       | 65 536                     |    |                                                          |

On s'intéresse au codage en base 2. Sur N positions,  $2^N$  naturels,  $[0, 2^N - 1]$ . ex sur 4 positions.

**Logarithme à base 2, nombre de bits** L'opération réciproque de l'élévation à la puissance s'appelle le logarithme. Ici, le logarithme à base 2. Ainsi si  $Y = 2^X$ , on a  $X = \log_2 Y$  Par exemple  $\log_2 512 = 9$  Pour représenter Y naturels différents, il faut  $\log_2 Y$  chiffres. (Attention aux arrondis à l'entier supérieur) Pour représenter les naturels de l'intervalle [0, ..., 9] il faut 4 bits, de même pour les naturels de l'intervalle [0, ..., 255] il faut 8 bits. Pour coder les naturels de [0, 127], il faut 7 bits.

Comment trouve-t-on les chiffres binaires de l'écriture d'un naturel? On parlera de chiffres des unités, DEUZAINES, QUATRAINES, huitaines, seizaines. (bien que ces mots ne soient pas tous dans le dictionnaire)

La méthode des restes successifs donnent les chiffres en commençant par celui des unités.

```

169 = 84 \times 2 + \boxed{1} \text{ (chiffre des unit\'es} = 1)

169 = (42 \times 2 + \boxed{0}) \times 2 + 1 \text{ (chiffre suivant} = 0)

169 = ((21 \times 2 + 0) \times 2 + 0) \times 2 + 1

169 = (((10 \times 2 + 1) \times 2 + 0) \times 2 + 0) \times 2 + 1

169 = ((((5 \times 2 + 0) \times 2 + 1) \times 2 + 0) \times 2 + 0) \times 2 + 1

169 = (((((2 \times 2 + 1) \times 2 + 0) \times 2 + 1) \times 2 + 0) \times 2 + 0) \times 2 + 1

169 = ((((((1 \times 2 + 0) \times 2 + 1) \times 2 + 0) \times 2 + 1) \times 2 + 0) \times 2 + 0) \times 2 + 1

```

On a donc  $169_{10} = 10101001_2$

Utilisation des puissances de 2 :

```

169 = 128 + 42

= 128 + 32 + 9

= 128 + 32 + 8 + 1

= 1*2^7 + 0*2^6 + 1*2^5 + 0*2^4 + 1*2^3 + 0*2^2 + 0*2^1 + 1*2^0

```

#### 1.4 Ecriture en base 16 ou base hexadécimale

Les 16 chiffres sont 0, 1, ..., 8, 9, A, B, C, D, E, F. Ils représentent respectivement les naturels qui s'écrivent 0, 1, ... 8, 9, 10, ..., 15 en décimal. On apprend par coeur le tableau suivant qui donne pour les nombres de 0 à 15 leurs écritures en base 10, 2 et 16 :

Passage d'une base à une autre (en relation de puissance) Technique pour passer de la base 2 à la base 8 (ou octale) ou 16. Technique pour passer de la base 16 ou 8 à la base 2.

$$\begin{array}{l} 169 = 10 \times 16 + 9 \\ 169_{10} = A9_{16} \\ 169_{10} = A_{16} \times 16_{10} + 9_{16} \\ 169_{10} = (((1 \times 2 + 0) \times 2 + 1) \times 2 + 0) \times 2^4 + (((1 \times 2 + 0) \times 2 + 0) \times 2 + 1) \\ 169_{10} = 1 \times 2^7 + 0 \times 2^6 + 1 \times 2^5 + 0 \times 2^4 + 1 \times 2^3 + 0 \times 2^2 + 0 \times 2^1 + 1 \times 2^0 \\ \text{On retrouve } 169_{10} = 10101001_2 \end{array}$$

On obtient cette écriture en "remplaçant", dans l'écriture en base 16, A par 1010 et 9 par 1001.

| base | x            | у            | z           | t            |

|------|--------------|--------------|-------------|--------------|

| 16   | 49D          | 8F0          | 008         | 55A          |

| 2    | 010010011101 | 100011110000 | 00000001000 | 010101011010 |

| 8    | 2235.        | 4360.        | 0010.       | 2532.        |

#### 1.5 Représentation des relatifs par des vecteurs binaires

#### 1.5.1 une première idée : signe et valeur absolue

esquisser l'algo de l'addition : compliqué...

#### 1.5.2 complément à deux

même algo pour add/sub naturels/relatifs. note: même algo = même circuit.

idée complément à 2 sur 8 bits : on peut représenter  $2^8 = 256$  infos différentes ; la moitié pour les positifs, la moitié pour les négatifs. On code les relatifs de l'intervalle [-128, +127], pas symétrique : le zéro... et surtout x+(-x)=0!!!

principe:

$$-x \ge 0$$

$x \in [0, +127]$  CodeC2(x)=x

$-x < 0$   $x \in [-128, -1]$  CodeC2(x)=x+256

En binaire, ca donne

| entier relatif | Code(base10)                        | CodeC2(base2) |

|----------------|-------------------------------------|---------------|

| -128           | 128                                 | 1000 0000     |

| -127           | 129                                 | 1000 0001     |

| -126           | 130                                 | 1000 0010     |

|                |                                     |               |

| -1             | 255                                 | 1111 1111     |

| 0              | 0                                   | 0000 0000     |

| 1              | 1                                   | 0000 0001     |

| 2              | 2                                   | 1000 0010     |

|                |                                     |               |

| 12             | 12                                  | 0000 1100     |

|                |                                     |               |

| 127            | 127                                 | 0111 1111     |

| D/ / 0 1       | $GO()$ $( \cdot \circ \circ \circ)$ | 1.050         |

Résumé:  $CodeC2(x)=(x+256) \mod 256$

Décodage :

- $-c < 128 \operatorname{decodeC2(c)} = c$

- $-c \ge 128 \operatorname{decodeC2(c)} = c-256$

Exercice: établir le tableau des codes des relatifs de l'intervalle [-8,+7] et de leur code représenté en base 10 et en base 2.

Où est le code? Soit le vecteur binaire 1001. Que représente-t-il? Si je ne vous donne pas la règle de codage, vous ne savez pas répondre. Il code une couleur (bleu pale) ou un naturel sur 4 bits (9) ou un relatif sur 4 bits (-7).

#### 1.6 Opérations

#### 1.6.1 Addition

rappel + en base 10 : retenue, propagation, taille résultat.

Un processeur fait ses calculs sur une taille donnée : c'est physique, il a pas prévu la place...

Interprétation du résultat : Si naturels 5+2=7, 5+3=8, 7+9=16, sur 4 bits  $n \in [0,+15]$ , 16 pas représentable, retenue C

Si relatifs 5+2=7, 5+3=-8???, 7+(-7)=0, sur 4 bits  $n \in [-8,+7]$ , 5+3 donne un résultat qui n'a pas de sens, il n'est pas représentable, dans le processeur indicateur pour donner cette info, indicateur V

## Chapitre 2

# Modèle de Von Neumann : Qu'est ce qu'un ordinateur

Dans tout notre travail: double vision:

- vision abstraite : des fonctions, des "entités", des modèles, des communications, des informations. Le modèle de définition de l'ordinateur a été élaboré entre 30 et 45 par Turing, Von Neumann, d'autres.

- vision concrète : où ça se passe, combien il y a de fils électriques, combien ça met de temps en secondes (ou en  $10^{-9}$  secondes).

Les premiers ordinateurs ont été construits entre 40 et 45, principalement pour des besoins militaires (calcul de balistique, décryptage,..)

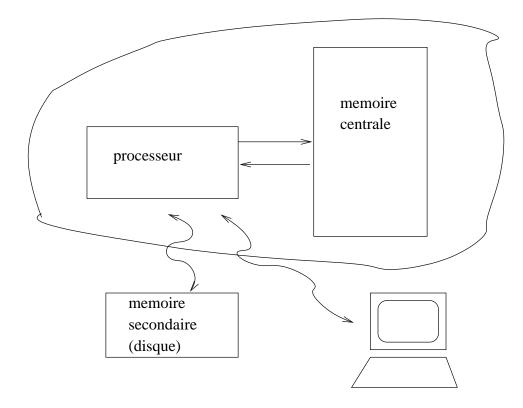

L'ordinateur (figure 2.1 exécute des programmes au moyen de 3 entités qui interagissent :

- processeur;

- mémoire centrale;

- système d'entrées-sorties (et liaison avec la mémoire secondaire) On parlera peu d'entrées-sorties en L2. C'est pour les grands de L3.

Le processeur exécute les programmes contenus dans la mémoire (centrale). Cette exécution a pour effet des actions vis à vis du monde extérieur via les périphériques. (disque, écran, imprimante..)

Les programmes traitent des REPRÉSENTATIONS des informations. Et les programmes SONT des informations. Dans les ordinateurs les informations sont représentées par des vecteurs binaires (vision abstraite), ce qui permet des connexions par des nappes de fils (vision physique) électriques au potentiel Haut ou Bas, selon l'instant.

## 2.1 Mémoire (sous-entendu centrale)

Les informations représentées par des vecteurs binaires peuvent être mémorisées. (Pour être consultées plusieurs fois)

#### 2.1.1 Définition

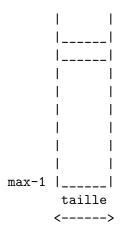

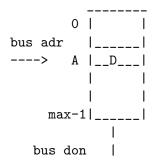

#### Vision abstraite, logique

La mémoire contient des informations (parmi un certain domaine) codées (vecteurs binaires d'une certaine taille), en certaine quantité, pouvant (peut-être) être modifiées et désignables par une certaine "adresse".

FIG. 2.1 – Processeur, mémoire et périphériques

Adresse = moyen de désigner une info dans la mémoire Adresse parmi [0, max-1], numéros d'emplacements. On parle d'emplacement précédent, suivant.

Une info en mémoire est représentée par un vecteur binaire d'une certaine taille (nombre de bits).

Nous verrons que l'on représente des infos :

- de taille 8 bits : octet (byte)

- de taille 16 bits : demi-mot (hword)

- de taille 32 bits : mot (word)

Si une info est à l'adresse X, l'octet suivant est à l'adresse X+1, le mot suivant est à l'adresse X+4. Les adresses sont exprimées en nombre d'octets.

Une adresse est aussi représentée sur un certain nombre de bits. Le numéro d'emplacement est codé par un vecteur binaire de  $(\text{Log}_2 \text{ max})$  bits. Par exemple 32 bits : cela permet de désigner  $2^{32}$  octets différents.

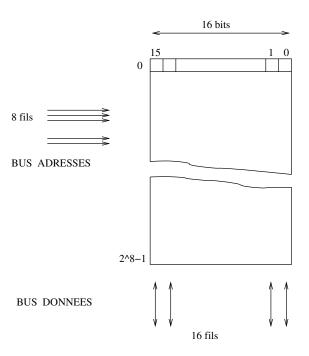

Fig. 2.2 - Mémoire physique d'info sur 16 bits avec addresses sur 8 bits

**Note :** remarquons que

$$2^10 = 1024 \approx 10^3$$

D'où  $2^{32} = 2^{10} \times 2^{10} \times 2^{10} \times 4 \approx 10^3 \times 10^3 \times 10^3 \times 4 = 4 \times 10^9$

#### Vocabulaire:

- $-1 \text{ kilo (octet)} = 10^3 \approx 2^{10}$

- $-1 \text{ méga (octet)} = 10^6 \approx 2^{20}$

- $-1 \text{ giga (octet)} = 10^9 \approx 2^{30}$

#### Vision physique

Toutes les infos sont représentées par des vecteurs binaires ce qui permet des connexions par des nappes de fils.

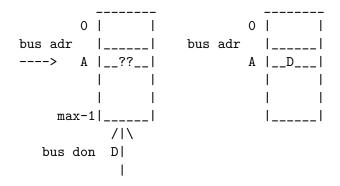

#### 2.1.2 Actions sur la mémoire

LIRE La mémoire reçoit un vecteur binaire représentant une adresse (notons A) sur le bus adresses et un signal de commande de lecture.

Elle délivre un vecteur binaire représentant la donnée (notons D) sur le bus données. Il s'agit du contenu de l'emplacement mémoire dont l'adresse est A.

On notera : D = mem [A]

#### ECRIRE La mémoire reçoit :

- un vecteur binaire (représentant une adresse A) sur le bus adresses,

- un vecteur binaire (représentant la donnée D) sur le bus données,

- un signal de commande d'écriture.

Elle inscrit (*peut-être*, voir tableau ci-après) la donnée D comme contenu de l'emplacement mémoire dont l'adresse est A.

On écrira : mem[A] >-- D

**NE RIEN FAIRE** : ni lecture, ni écriture. La mémoire garde indéfiniment (*peut-être*, voir tableau ci-après) les informations.

La lecture et l'écriture ne peuvent pas être simultanées. On dit que le bus données est "bidirectionnel" mais c'est dans le temps. A un instant donné ce n'est pas vrai.

#### 2.1.3 Différents types; vision très concrète

| nom du type de mémoire | propriété de sauvegarde | propriété de modifiabilité            |

|------------------------|-------------------------|---------------------------------------|

|                        | si coupure de courant   | selon type d'utilisateur              |

| ROM mémoire morte      | garde l'info            | inscrite à la fabrication             |

|                        |                         | usine de fabrication semi-conducteurs |

| Eprom (+ variantes)    | garde l'info            | modifiable (100 fois)                 |

|                        |                         | atelier PMIPME électronique           |

| mémoire "flash"        | garde l'info            | modifiable 100 000 fois               |

|                        |                         | utilisateur dans appareil             |

|                        |                         | carte bancaire, téléphone, vitale     |

| RAM mémoire vive       | perd l'info             | modifiable autant de fois             |

|                        | si coupure de courant   | que le signal écriture sera activé    |

| mémoire cache          | rien à voir             | dans cette classification             |

#### 2.2 Entrées sorties

Le processeur peut accéder à divers organes physiques, clavier, disque, réseau, écran, d'interaction avec l'utilisateur, de communication ou de stockage. Des informations peuvent être échangées (dans un ou deux sens) entre ces organes et la mémoire.

#### 2.3 Processeur

#### 2.3.1 Actions, processeur/mémoire

Le processeur est un circuit relié à la mémoire par les bus adresses et données.

La mémoire contient des informations de nature différentes :

- des données : représentation binaire d'une couleur, d'un entier, d'une date, etc.

- des instructions : spécification écrites en binaire d'une ou plusieurs actions que le processeur peut exécuter; par exemple, ajouter le contenu de deux mots mémoire et ranger le résultat à une adresse précise.

Le processeur, lié à une mémoire, peut :

- lire un mot : le processeur fournit une adresse, un signal de commande de lecture et reçoit le mot.

- écrire un mot : le processeur fournit une adresse ET une donnée et un signal de commande d'écriture.

- ne pas accéder à la mémoire.

- EXÉCUTER des instructions, ces instructions étant des informations lues en mémoire.

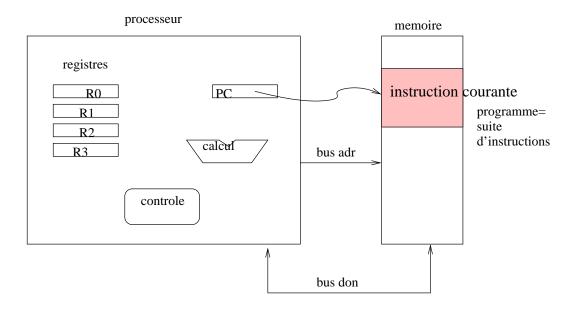

#### 2.3.2 Composition du processeur

Le processeur est composé d'unités (ressources matérielles internes):

- des registres cases de mémoire interne désignées par des numéros ou des noms particuliers. A la différence des emplacements mémoire (centrale), peuvent être lus et écrits simultanément (et même, peuvent être écrits avec une valeur qui est fonction de la valeur qui y était précédemment). L'action REG < REG + 1 est atomique sur les registres.

- des unités de calcul élaborent un vecteur binaire à partir d'un (ou plusieurs) vecteur(s) binaire(s) présenté(s) en entrée (représentant une "valeur" et, peut-être, une commande).

- exemple : additionneur 8 bits. dessin 2 nappes de 8 fils en entrées, 1 nappe de 8 fils en sortie, + des sorties donnat des infos sir la correction du résultat.

- une unité de contrôle elle aussi contient registres et unités de calcul. Mais ses "résultats" (sorties) sont des ordres, ou successions d'ordres, émis vers les registres, unités de calcul, et mémoire. Son rôle est d'enchaîner des actions de base, par ex faire faire 2 additions de suite. L'exécution des instructions consiste précisemment à émettre de telles successions d'ordres.

- un compteur ordinal ou compteur programme (PC) ou pointeur d'instructions Ce registre particulier repère l'adresse en mémoire de l'instruction en cours d'exécution.

#### 2.3.3 Notion d'exécution séquentielle des instructions

Pour ex'ecuter une suite d'instructions (on appelle une telle suite un programme) le processeur effectue de façon cyclique :

- lire une instruction à l'adresse contenue dans PC

- exécuter cette instruction

- calculer l'adresse de l'instruction suivante et mettre à jour PC

Dans un ordinateur cette boucle démarre par un signal physique (RESET) qui a pour effet de forcer une valeur initiale dans PC et ne s'arrête jamais (sauf coupure de courant...). Il peut dans les machines modernes être suspendu pour économiser de l'énergie (machines portables, embarquées,...)

Normalement les instructions sont exécutées dans l'ordre où elles sont écrites en mémoire. Certaines instructions spécifiques donnent l'adresse de l'instruction suivante (rupture de séquence). On y reviendra.

FIG. 2.3 – Processeur relié à de la mémoire

#### 2.3.4 Notion élémentaire de langage machine : première définition

La nature de l'instruction c'est-à-dire des actions à réaliser par le processeur est CODÉE dans un (ou plusieurs) mots de l'instruction.

Le codage des instructions par des vecteurs binaires constitue le  $langage\ machine\ du\ processeur.$  On parle :

- D'ARCHITECTURE LOGICIELLE pour décrire l'organisation du langage machine, ISA=Instruction Set Architecture

- D'ARCHITECTURE MATÉRIELLE pour décrire la façon dont il est exécuté par du matériel.

#### 2.3.5 C'est quoi les processeurs?

Sur les PC : des pentium, ou des compatibles. Sur les Macintosh : 68000 (très anciens) ou PowerPC (anciens) ou Pentium (récents), Sur certaines consoles de jeux : des ARM (le même qu'on étudiera en TP)

## Chapitre 3

# Langage d'assemblage, langage machine

#### 3.1 Vie d'un programme

timing : Ce chapitre prend un peu plus d'une séance d'1h30. Le suivant par contre (rupture de séq et sous-programme) est un peu plus court.

#### Etapes de compilation

- 1. monprog.c contient des instructions du langage C + données par exemple les chaînes de caractères (cf tp avec la chaîne charlot)

- 2. gcc -S monprog.c ou arm-elf-gcc -S monprog.c produit monprog.s qui contient des instructions du lg d'assemblage + données : on va y revenir ; lisible par un éditeur de texte (mais non exécutable)

- 3. gcc monprog.s -o monprog produit monprog qui contient des instructions en langage machine + données; non lisible mais exécutable. On dit que le fichier contient du binaire exécutable. remarque : ne pas confondre exécutable, lié à la nature du fichier, et "muni du droit d'être exécuté", lié au système d'exploitation. remarque : il y a une étape supplémentaire, la production du fichier monprog.o qui contient du binaire dit translatable, non directement exécutable; on y reviendra dans un chapitre ultérieur.

Le binaire exécutable contient des instructions codées en binaire et pouvant être traitées, exécutées par un processeur.

#### Comment exécuter monprog? Plusieurs classes d'ordinateurs.

- On est sur un ordinateur (PC, station Solaris) dont le binaire est connu du processeur (ex on a produit du "binaire Intel", on est sur un PC dont la carte mère est équipée d'un processeur Intel, avec une commande comme gcc monprog.c). On tape monprog ou on "double clique" dessus. Une partie du Syst.Exploit. copie le contenu du fichier exécutable du disque dur vers la mémoire centrale, puis met l'adresse de début dans le registre PC et ensuite le matériel (le processeur) fait son boulot...

- C'est le Syst.Exploit. qui choisit l'emplacement en mémoire centrale et NOUS ne le connaissons pas (on va négliger l'aspect mémoire virtuelle...)

- Connaissance pas utile de l'architecture matérielle fine. Le programme sera mis n'importe où, et çà marche quand même.

- On est sur un ordinateur qui ne connait pas le binaire que l'on produit (ex. arm-elf-gcc monprog.c produit du binaire arm et on est sur un Intel). On utilise un simulateur, c'est-à-dire un programme qui fait semblant d'exécuter ce binaire (arm-elf-run monprog). Le simulateur réalise des actions équivalentes aux instructions du programme dans une mémoire à lui.

- Cas des automatismes (lecteur de carte électronique, etc.) Quand on écrit le programme on connaît précisément l'architecture et on peut produire directement une image du programme dans la mémoire à une adresse fixe et ranger le binaire dans une EPROM (une mémoire qui garde l'info quand on coupe le courant).

#### 3.2 Langage machine

Pour tout processeur il existe UN langage machine caractéristique. (compatibilité entre processeurs dérivés, famille,..)

Comme tout langage (informatique ou non) le LM a

- un lexique : les mots que l'on peut écrire

- une syntaxe : l'organisation des mots qui est permise

- une sémantique : le sens des phrases, cad des succession de mots

Un peu plus en "détail":

- un lexique et une morphologie : la liste des mots du langage (les instructions), la façon dont ils s'écrivent (leur codage) , éventuellement les variantes, les groupements d'instructions d'une même famille, etc Pour le LM les mots sont des suites de 0 et de 1. On remarque au passage que si votre numéro de sécurité sociale qui traine qqpart en mémoire est AUSSI le code d'une certaine instruction, si le compteur ordinal du processeur, à la suite d'une erreur, se met à "pointer" là, il se peut que votre numéro de sécu soit "exécuté". sinon... voir ci-après, cas de fautes.

- une syntaxe quels sont les groupements valides d'instructions en programmes? C'est, en général, très souple : on peut écrire ce qu'on veut... Pour le LM, la syntaxe dit que les suites de 0 et de 1 sont organisées par champs pour former des instructions.

- une sémantique (signification) Un programme est une suite (ou séquence, liste) d'instructions, il y a un ORDRE. Les instructions sont exécutées dans l'ordre où elles sont écrites. Vu de l'extérieur si on considère un processeur dans lequel chaque instruction est codée sur 32 bits, un programme est une séquence de mots de 32 bits. Un mot de 32 bits représente 1 instruction c'est-à-dire un ordre à faire exécuter par le processeur. Par exemple, l'instruction 36842 précise qu'il faut ajouter le nombre actuellement dans le registre 17 avec celui qui est dans le registre AB et ranger le résultat en mémoire à l'adresse 27.

- un dictionnaire des fautes! Si il y a 237 instructions dans le langage machine d'un certain processeur, elles peuvent être codées par un vecteur binaire de 8 bits (2<sup>7</sup> = 128; 2<sup>8</sup> = 256) et donc il y a 19 vecteurs invalides. Que doit alors faire le processeur s'il rencontre un code invalide?

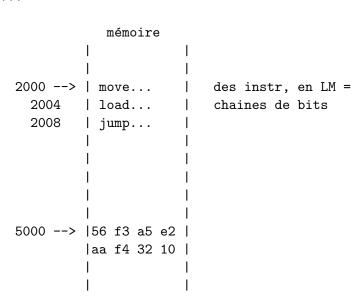

## 3.3 Instructions et programmes en langage machine

Nous sommes débutants : nous nous plaçons dans l'hypothèse du cas où en écrivant l programme, on sait à quelle adresse le programme sera rangé en mémoire pour être exécuté (instructions et données) mais attention, en TP avec le processeur ARM et le simulateur utilisé, ça ne sera pas le cas.

Par ailleurs nos instructions, nous les écrivons en français, plus lisible que le binaire. les données, pareil, nous écrivons des caractères ASCII, des nombres,...

2 types principaux : instructions de calcul (ou d'échanges de place) entre des informations mémorisées et instructions de rupture de séquence.

## 3.3.1 Instructions de calcul (ou d'échanges de place) entre des informations mémorisées.

L'instruction désigne alors la source et le destinataire. Les "sources" sont des éléments de mémorisations : cases mémoires ou registres du processeur. Le destinataire sera pareil.

L'instruction désigne destinataire, source1, source2, opération. on a les combinaisons suivantes

|     | désignation     |     |              |     | désignation |     | désignation |     |        |

|-----|-----------------|-----|--------------|-----|-------------|-----|-------------|-----|--------|

|     | du destinataire |     | $\leftarrow$ |     | de source1  |     | de source2  |     |        |

| mém |                 | reg |              | mém |             | reg | mém         | reg | valIMM |

mém signifie que l'instruction fait référence à une case dans la mémoire

reg signifie que l'instr fait référence à un registre (par son nom ou son numéro)

valIMM signifie que l'information source est contenue dans l'instruction du langage machine.

#### Exemples de signification d'instructions, peu importe le codage :

- $\operatorname{reg} 12 \leftarrow \operatorname{reg} 14 + \operatorname{reg} 1$

- registre4 ← le mot mémoire d'adresse 36000 PLUS le registre A

- $\operatorname{reg5} \leftarrow \operatorname{reg5} 1$

- le mot mémoire d'adresse 564 ← registre7 (opération : rien du tout)

- CONVENTIONS de NOMS : move, load, store

#### 3.3.2 Instructions de rupture de séquence

On y reviendra en détail.

Fonctionnement standard : une instruction est écrite à l'adresse X ; l'instruction suivante (dans le temps) est l'instruction écrite à l'adresse X+(taille de l'instruction). C'est implicite pour toutes les instructions de calcul.

Une instruction de *rupture de séquence* peut désigner la prochaine instruction à exécuter (à une autre adresse).

#### Exemples:

- L'instr. suivante est celle d'adresse 5012. La suivante de l'instruction II peut même être II, mais alors le processeur part en boucle non contrôlée. Il faut utiliser Reset.

- L'instr. suivante est celle rangée à l'adresse "mon adresse" MOINS 40 (ou "mon adresse" PLUS 10). Note: cela peut servir à "faire" des boucles, répéter le même paquet d'instructions plusieurs fois (dessins...)

- Si le résultat du calcul précédent est ZERO, alors la prochaine instr. à exécuter est celle d'adresse "mon adresse+10", sinon la prochaine instr. à exécuter est la suivante dans l'ordre d'écriture, cad à l'adresse "mon adresse"+1. Utilisation : codage de choix.

#### 3.3.3 Remarques:

- 1. une instr. du LM est une chaine de bits. Pour en parler on a écrit en "français". On aurait besoin d'une correspondance : instr. en français chaine de bits (LM écrit en binaire)

- 2. lorsque l'on considère une chaine de bits (pax ex 1 mot de la mémoire) on ne sait pas si elle représente une donnée (un naturel, un relatif, une couleur, un caractère, ...) ou une instruction. Le code n'est pas dans l'info codée!!!

- 3. on a vu plusieurs instructions qui tiennent compte de la place réelle en mémoire des données ou instructions. Quand on ne connaît pas ces emplacements (les adresses), que faire?

#### 3.4 Langage d'assemblage

On introduit un niveau de langage plus facile à manipuler, à lire :

- langage textuel (au lieu de binaire) mais correspondance 1 instruction Lg Ass  $\leftrightarrow$  1 instruction Lg machine

- claire séparation données, instructions

- on ne connait pas les adresses réelles, on ne peut donc pas en tenir compte.

#### 3.4.1 Langage textuel, notation des instructions

1 instruction = mot conventionnel (mnémonique) + désignation des objets (instr ou données) manipulés. A chaque notation est associée une convention d'interprétation).

#### Exemples:

- machine1 (ARM): add r4, r5, r6 signifie  $r4 \leftarrow r5 + r6$ . r4 désigne le contenu du registre, on parle bien sur du *contenu* des registres, on n'ajoute pas des ressources physiques

- machine 2 (SPARC): add %g4, %g5, %g6 signifie  $g6 \leftarrow g4 + g5$

- machine 3 : addA 5000 signifie regA  $\leftarrow$  regA + Mem[5000]

- machine 3: addA  $\sharp$ 50 signifie regA  $\leftarrow$  regA + 50

- machine 4: add r3, r3, [5000] signifie reg3  $\leftarrow$  reg3 + Mem[5000]

Remarque: Il n'y a pas de règle (notation) générale, cela dépend des fabricants. Il y a juste qq habitudes concernant les mnémoniques (add, sub, load, store, jump, branch, clear, inc, dec) ou la notation des opérandes (#, [xxx]) mais rien de général...

#### 3.4.2 Désignation des objets

On parle parfois, improprement, de modes d'adressage. Il s'agit de dire comment on écrit par exemple la valeur contenue dans le registre numéro 5, la valeur -5, la valeur rangée dans la mémoire à l'adresse 0xff, etc.

Il n'y a pas de standard de NOTATIONS, mais des standards de SIGNIFICATION d'un constructeur à l'autre.

L'objet désigné peut être une instruction ou une donnée.

#### Définitions (à connaître :)

- désignation par registre L'objet désigné, une donnée, est le contenu d'un registre. L'instruction contient le nom ou le numéro du registre.

- -6502:2 registres A et X (entre autres) TAX = transfert de X dans A = contenu de X  $\leftarrow$  contenu de A (on écrira X leftarrow A). Désignations registre, registre.

- ARM : mov r4 , r5; signifie r4  $\leftarrow$  r5. Désignations registre, registre.

- désignation immédiate La donnée dont on parle est "carrément" incluse dans l'instruction (tjrs des données)

- ARM: mov r4, #5; signifie r4  $\leftarrow$  5. Désignations registre, immédiate.

- désignation directe ou absolue L'objet désigné est dans une case mémoire dont on donne l'adresse dans l'instruction. L'objet désigné peut être une instr ou une donnée.

- machine 1 : store R4, [5000] = Mem[5000] ← R4. Désignations registre, directe ou absolue.

le deuxième opérande (ici une donnée) est désigné par son adresse en mémoire.

- machine 2 : jump 0x2000 : l'instruction suivante (qui est l'instruction que l'on veut désigner) est celle d'adresse 0x2000.

- désignation indirecte par registre L'objet désigné est dans une case mémoire dont l'adresse est dans un registre précisé dans l'instruction.

- ARM: add r3,  $[r5] = r3 \leftarrow r3 + le$  mot mémoire dont l'adresse est contenue dans le registre 5; on note souvent  $r3 \leftarrow r3 + mem[r5]$ . Dessin... Désignations registre, indirect par registre

- désignation indirecte par registre et déplacement L'adresse de l'objet désigné est obtenue en ajoutant le contenu d'un registre précisé dans l'instruction et d'une valeur (ou d'un autre registre) précisé aussi dans l'instruction.

- ARM: add r3, [r5, #4] =  $r3 \leftarrow r3 + mem[r5 + 4]$ . Dessin... la notation [r5 + #4] désigne le mot mémoire (une donnée ici) d'adresse r5 + #4].

- machine 3 jump [PC 12]: le registre est PC, le déplacement -12. L'instruction suivante (qui est l'instruction que l'on veut désigner) est celle à l'adresse obtenue en calculant, au moment de l'exécution, PC 12. Quand le registre est PC on parle de désignation relative au compteur de programme PC.

#### 3.4.3 Séparation données instructions

Le texte du programme est organisé en zones :

- zone TEXT : code, programme, instructions, constantes

- zone DATA : données initialisées

- zone BSS: données non initialisées, reservation de place en mémoire

Parfois on peut préciser où chaque zone doit être placée en mémoire : directive ORG pour donner l'adresse de début de la zone.

On prend cette hypothèse pour l'exemple suivant, dans lequel on suppose que les instructions sont toutes codées sur 4 octets :

```

zone TEXT, org 0x2000

move r4, #5004

load r5, [r4]

jump 0x2000

.....

zone DATA, org 0x5000

entier sur 4 octets : 0x56F3A5E2

entier sur 4 octets : 0xAAF43210

....

```

effet de ce programme : mettre 0xAAF43210 dans r5 et recommencer indéfiniment. Ce qui est très utile..

#### 3.4.4 Etiquettes

#### 2 raisons:

- si on ne sait pas l'emplacement de chargement des programmes (la directive ORG ne peut pas toujorus être utilisée)

- si on veut se faciliter la vie

**Définition : Etiquette** = nom choisi librement (il y a des règles lexicales quand même) qui désigne une case mémoire. cette case peut contenir une donnée ou une instruction, D'où une étiquette correspond à une adresse.

#### Exemple:

```

zone TEXT

DD: move r4, #5004

load r5, [YY]

jump DD

zone DATA

XX: entier sur 4 octets : 0x56F3A5E2

YY: entier sur 4 octets : 0xAAF43210

```

#### Avantages:

- Le programmeur n'a pas besoin de connaître ces VRAIES adresses pour comprendre ce que fait son programme...

- Le programme est plus facile à lire, à écrire

#### Quand la correspondance étiquette/adresse est-elle faite?

- Le remplacement de DD par 2000 et de YY par 5004 est fait au moment de l'assemblage sur les machines où l'adresse de chargement est connue au moment de l'assemblage (si les adresses de chargement des zones TEXT et DATA sont respectivement 2000 et 5000). De plus en plus rare. L'adresse de chargement peut être connue de l'outil ou passée en paramètre lors de l'appel de l'assemblage.

- la correspondance peut aussi être faite lors de la phase d'implantation en mémoire (on parle de chargement) si l'adresse de chargement N'est PAS connue au moment de l'assemblage.

## Chapitre 4

# Instructions de rupture de séquence et Programmation des structures de contrôle

#### 4.1 Exécution séquentielle et ruptures de séquences

On se souvient du rôle du compteur programme (PC).

#### 4.1.1 Exécution séquentielle et ruptures de séquences

Il existe un registre spécial du processeur : le compteur programme PC (ou pointeur d'instructions IP).

A chaque instruction le proc émet une copie du contenu de PC sur le bus adresses, récupère l'instruction fournie sur le bus données. Il l'exécute (on verra comment plus tard). Il met à jour le PC pour préparer l'accès à l'instruction suivante. Par défaut en l'incrémentant.

Et ca recommence...

Ainsi les instructions écrites dans la mémoire sont exécutées dans l'ordre d'écriture. SAUF ... instructions de rupture de séquence.

Regardons les 8 cas de séquencement :

- 1. A l'initialisation, PC est forcé à une valeur pré-établie (0)

- 2. **Séquencement normal** Après chaque instruction le PC est incrémenté. De 1 si l'instruction est codée sur UN seul mot, parfois sur plusieurs. Ca dépend des machines et des instructions et de la taille des mots.

- REMARQUE sur ARM, qui est une machine où toutes les instructions ont la même longueur, le compteur programme progresse d'instructions en instructions. Comme les adresses sont des adresses d'octets et que les instructions sont sur 4 octets, le PC progresse de 4 en 4

- à contrario sur certaines machines où les instructions sont de longueur variable, par exemple,

1, 2, ou 3 octets, le PC donne successivement les adresses des différents octets de l'instruction.

On y reviendra quand on étudiera l'exécution détaillée.

- 3. Rupture inconditionnelle : L'exécution d'une instruction consiste à forcer une nouvelle valeur dans le PC.

- Cas TRES particulier : certains des premiers RISC (dont le Sparc, le mips, ...) exécutent quand même l'instruction qui suit le saut. C'est bizarre, c'est comme ça... Il y a des raisons,

- 4. Rupture conditionnelle : si la condition <sup>1</sup> est vérifiée, le PC est modifié, sinon il progresse de 1 comme normalement. (ou de 4...)

<sup>&</sup>lt;sup>1</sup>Condition en général interne au processeur, parfois externe

- 5. Appels retour de sous programmes : On va y revenir tout de suite.

- 6. **Interruptions** Un mécanisme essentiel, mais pour les grands. Si un certain signal PHYSIQUE externe est actif, PC prend une valeur lue en mémoire à une adresse conventionnelle.

- 7. Machine superscalaire Exécute plusieurs instructions "en même temps" cours d'architecture avancée

- 8. Instructions de séquencement exotiques cours d'architecture avancée.

#### Désignation de l'instruction suivante

- Désignation directe : l'adresse de l'instruction suivante est donnée dans l'instruction. Exemple dans le processeur utilisé pour le TD automate il y a des JUMP qui sont comme ça

- Désignation relative : l'adresse de l'instruction suivante est obtenue en ajoutant un certain déplacement (peut être signé) au compteur Programme.

Remarque: On est souvent dérouté par le fait que le déplacement est ajouté par rapport à l'adresse de l'instruction qui suit la rupture. On verra pourquoi en étudiant en détail le véritable séquencement (Chapitre 7).

C'est le cas sur ARM.

**Exemple:** machine à instructions sur 4 octets

| etiquette | adresse correspondant | instruction ASS   | codage effectif de |

|-----------|-----------------------|-------------------|--------------------|

|           | a l'etiquette         |                   | l'instruction      |

|           | 0x1028                | CLR Reg6          | 0x******           |

| e1:       | 0x102C                | BRANCH si cond e2 | $0x^{****} + 0x0C$ |

|           | 0x1030                | xxx               | XXX                |

|           | 0x1034                | xxx               | XXX                |

|           | 0x1038                | xxx               | XXX                |

| e2:       | 0x103C                | ууу               | 0x******           |

|           | 0x1040                | xxx               | XXX                |

|           | 0x1044                | xxx               | xxx                |

(0x102C + 4 + 0x0C = 0x103C)

#### Utilisation typique des sauts ou branchements

On se place du point de vue de la programmation en langage d'assemblage, et de façon SYSTÉMATIQUE.

On va considérer la programmation de 3 types de construction algorithmiques :

- programmation systématique des structures de contrôle de la programmation classique (type if then else)

- programmation systématique des solutions modélisées par des automates avec actions (automates étendus de INF232) (on dira aussi machines séquentielles avec actions)

- programmation systématique des sous-programmes (procédures et fonctions).

On commence ici par les structures de contrôle classiques de la programmation impérative?

- Action0; if (cond) then (Action1); Action2

- Action0; if (cond) then (Action1) else Action2; Action3

- Action0; while (cond) (Action1); Action2; Action3

- Action0; repeat (Action1) until (cond); Action2; Action3

- Action0; for (i=0; i<N; i++) Action2; Action3;; Action4

- Action0; for (i=N; i>=0; i- Action2; Action3; Action4

- Action0; if (cond1 ET cond2) then (Action1); Action2

- Action0; if (cond1 ETpuis cond2) then (Action1); Action2

- Action0; if (cond1 OU cond2) then (Action1); Action2

- Action0; if (cond1 OUalors cond2) then (Action1); Action2

On dispose seulement des sauts et des sauts conditionnels : branch etiq et branch si cond etiq.

#### 4.2 Conditionnelles

#### 4.2.1 Version Paul

Action0; si cond alors {Action1; Action2}; Action3

| etiquette    | adresse correspondent |                                 | codage de     |

|--------------|-----------------------|---------------------------------|---------------|

|              | a l'etiquette         |                                 | l'instruction |

|              | 0x1020                | fin de Action0                  | 0x******      |

|              | 0x1024                | calcul                          | 0x******      |

|              | 0x1028                | Evaluer cond dans FLAGS         | 0x******      |

|              | 0x102C                | BRANCH si cond debutdeact1      | 0x****        |

|              | 0x1030                | JMP debutdeaction3              | cible: 0x106C |

| debutdeact1: | 0x1034                | premiere instruction de Action1 | 0x******      |

|              | 0x1040                | XXX                             | XXX           |

|              | 0x1044                | XXX                             | XXX           |

| findeact1:   | 0x1048                | derniere instruction de Action1 | •••           |

| debutdeact2: | 0x1050                | premiere instruction de Action2 | ••            |

|              |                       | il pourrait y en avoir d'autres | •••           |

| findeact 2:  | 0x1054                | derniere instruction de Action2 | •••           |

|              |                       |                                 |               |

| debutdeact3: | 0x106C                | premiere instruction de Action3 | •••           |

|              | 0x1070                | suite de Action3                |               |

| findeact 2:  |                       |                                 |               |

Action0; si cond alors Action1 sinon Action2; Action3

| etiquette    | adresse correspondant | instruction ASS                 | codage de     |

|--------------|-----------------------|---------------------------------|---------------|

|              | a l'etiquette         |                                 | l'instruction |

|              | 0x1020                | fin de Action0                  | 0x******      |

|              | 0x1024                | calcul                          | 0x******      |

|              | 0x1028                | Evaluer cond dans FLAGS         | 0x******      |

|              | 0x102C                | BRANCH si cond debutdeact1      | 0x****        |

|              | 0x1030                | premiere instruction de Action2 |               |

|              |                       | il pourrait y en avoir d'autres |               |

|              | 0x1034                | derniere instruction de Action2 |               |

|              | 0x1038                | JMP debutdeact3                 | 0x0x104C      |

| debutdeact1: | 0x103C                | premiere instruction de Action1 | 0x******      |

|              | 0x1040                | xxx                             | XXX           |

|              | 0x1044                | XXX                             | xxx           |

| findeact1:   | 0x1048                | derniere instruction de Action1 |               |

| debutdeact3: | 0x104C                | premiere instruction de Action3 | •••           |

|              | 0x1050                | suite de Action3                |               |

#### VERSION 2 Action0; si cond alors Action1 sinon Action2; Action3

(En effet les conditions sur les codes de conditions arithmétiques vont souvent 2 par 2. L'une porte sur une condition et l'autre sur la condition complémentaire. cf doc du processeur quelqu'il soit.

| etiquette    | adresse correspondant | instruction ASS                 | codage de     |

|--------------|-----------------------|---------------------------------|---------------|

|              | a l'etiquette         |                                 | l'instruction |

|              | 0x1020                | fin de Action0                  | 0x******      |

|              | 0x1024                | calcul                          | 0x******      |

|              | 0x1028                | Evaluer cond dans FLAGS         | 0x******      |

|              | 0x102C                | Branch si NON cond debutdeact2  | 0x****        |

|              | 0x1030                | premiere instruction de Action1 |               |

|              |                       | il pourrait y en avoir d'autres |               |

|              | 0x1034                | derniere instruction de Action1 |               |

|              | 0x1038                | JMP debutdeact3                 | 0x0x104C      |

| debutdeact2: | 0x103C                | premiere instruction de Action2 | 0x******      |

|              | 0x1040                | XXX                             | xxx           |

|              | 0x1044                | xxx                             | xxx           |

| findeact 2:  | 0x1048                | derniere instruction de Action2 |               |

| debutdeact3: | 0x104C                | premiere instruction de Action3 |               |

|              | 0x1050                | suite de Action3                |               |

#### 4.2.2 Version Fabienne

On note Ik une instruction ; pour fixer les idées on peut penser que cela peut être une affectation mais cela peut être n'importe quelle instruction complexe ou séquence d'instructions.

#### I1; si ExpCond alors {I2; I3; I4}; I5

Par exemple ExpCond est A=B avec A et B deux entiers rangés respectivement dans les registres R1 et R2.

```

I1

calcul de A-B + positionnement de ZNCV

branch si non égal à 0 = non(Z) à etiq_suite

I2

I3

I4

etiq_suite: I5

```

Avec des adresses et des instructions de machines existantes codées sur 32 bits.

| 0x1020 | I1            | I1                      |

|--------|---------------|-------------------------|

| 0x1024 | CMP R1, R2    | CMP R1, R2              |

| 0x1028 | JUMP_ABS_1038 | BRANCH_RELATIF+12octets |

| 0x102c | 12            | 12                      |

| 0x1030 | 13            | 13                      |

| 0x1034 | 14            | 14                      |

| 0x1038 | I5            | I5                      |

**Note :** les 12 octets sont à moduler selon la valeur de PC au moment de l'exécution du branchement. Autre codage :

```

I1

calcul de A-B + positionnement de ZNCV

branch si égal à 0 = Z à etiq_alors

branch à etiq_suite

etiq_alors: I2

13

14

etiq_suite: I5

I1; si ExpCond alors {I2; I3} sinon {I4; I5; I6}; I7

Ι1

évaluer ExpCond + ZNCV

branch si faux à etiq_sinon

13

branch inconditionnel etiq_finsi

etiq_sinon: I4

15

16

etiq_finsi: I7

Autre solution:

Ι1

évaluer ExpCond + ZNCV

branch si vrai à etiq_alors

14

15

16

branch inconditionnel etiq_finsi

etiq_alors: I2

13

etiq_finsi: I7

```

Quand et comment l'adresse cible du branchement ou le déplacement correspondant sont-ils calculés? Par le traducteur (assembleur) lors du passage prog.s à prog.o. Soit il connait l'adresse de début et il associe une adresse à chaque instruction, soit il ne la connait pas et il calcule une différence (il connait la taille nécessaire au codage de chaque instruction en langage machine).

#### 4.3 boucles

```

4.3.1 I1; while ExpCond do {I2; I3}; I4

I1

debut: evaluer ExpCond

branch si faux fintq

I2

```

```

I3

branch toujours debut

fintq: I4

Ι1

branch toujours etiqcond

debutbcle: I2

etiqcond:

evaluer ExpCond

branch si vrai debutbcle

fintq:

I1; répéter {I2; I3} jusqu'à ExpCond; I4

I1

debutbcle: I2

evaluer ExpCond

branch si faux debutbcle

14

```

Observer les différences entre ce codage et la solution du tantque avec test à la fin.

#### 4.3.3 I1; for (i=0; i<N; i++) {I2; I3; I4}; I5

Traduire en tantque puis traduire en ARM (en exo...)

```

i=0

mov RO, #0

tantque i<N

tq: cmp RO, R1

@ N dans R1

12

bge ftq

Ι3

I3

14

Ι3

14

i=i+1

add RO, RO, #1

I5

bal tq

ftq: I5

```

Exercice: deux boucles for imbriquées

```

for (i=0; i<N; i++)

for (j=0; i<K; j++)

I2;I3

```

#### 4.4 Conditions non élémentaires

#### 4.4.1 si C1 ou C2 ou C3 alors I1; I2 sinon I3

Solution avec évaluation minimale des conditions, dite oualors en algorithmique.

```

evaluer C1

branch si vrai etiq_alors

evaluer C2

```

```

branch si vrai etiq_alors

evaluer C3

branch si faux etiq_sinon

etiq_alors: I1

12

branch toujours etiq_fin

etiq_sinon: I3

etiq_fin:

ou

evaluer C1

branch si vrai etiq_alors

evaluer C2

branch si vrai etiq_alors

evaluer C3

branch si vrai etiq_alors

etiq_sinon: I3

branch toujours etiq_fin

etiq_alors: I1

```

12

etiq\_fin:

Si on veut tout évaluer : évaluer chaque Ci dans un registre et utiliser l'instruction OR du processeur.

#### 4.4.2 si C1 et C2 et C3 alors I1; I2 sinon I3

Solution avec évaluation minimale des conditions, dite etpuis en algorithmique.

evaluer C1

branch si faux etiq\_sinon

evaluer C2

branch si faux etiq\_sinon

evaluer C3

branch si faux etiq\_sinon

etiq\_alors: I1

I2

branch toujours etiq\_fin

etiq\_sinon: I3

etiq\_fin:

## 4.5 Codage d'un choix

selon a,b:

a<b : I1

a=b : I2

a>b : I3

Une solution consiste à traduire en si alors sinon.

```

si a<b alors I1

sinon si a=b alors I2

sinon si a>b alors I3 (le test a>b est inutile...)

```

Spécifique ARM : instructions ARM conditionnelle. Dans le codage d'une instruction il est prévu un champ condition (bits 31 à 28) contenant un des mnémoniques des conditions. La sémantique d'une instruction est est la suivante : si la condition est vraie exécuter l'instruction sinon passer à l'instruction suivante (dans l'ordre d'écriture).

Ces instructions conditionnelles peuvent aussi être utilisées pour supprimer les branchements dans des if then else à corps-alors et corps-sinon de petite taille.

Réfléchir : il existe addeqs...

#### 4.6 Exercice de synthèse : nombre de 1

```

x, nb : des entiers >= 0

nb=0

tantque x <> 0

si \times mod 2 \iff = alors nb=nb+1

x = x div 2

.text

.global main

@ nb : r0

0 x : r1

main:

mov r1, #0xE2

mov r0, #0

tq: cmp r1, #0

beq ftq

tst r1, #1

beq suite

add r0, r0, #1

suite:

mov r1, r1, lsr #1

bal tq

ftq:

@ ecrire le contenu de r0

mov r1, r0

bl EcrNdecimal8

fin: bal exit

```

## Chapitre 5

# Programmation à partir des automates reconnaisseurs

# 5.1 Automate avec actions à nombre fini d'états : Définition commentée

Un automate avec actions à nombre fini d'états (on dit aussi un automate d'état fini étendu) est la donnée de :

- Un ensemble E (non vide, fini) nommé le **vocabulaire d'entrée** dont les éléments sont les **symboles** d'entrées. On appelle parfois E le "vocabulaire" terminal  $V_T$ . Les entrées peuvent aussi être des conditions portant sur les valeurs de variables.

- Un ensemble S (non vide, fini) dont les éléments sont appelés les états.

- Un élément particulier  $s_0$  de S qui est identifié comme l'état initial.

- Un ensemble O (non vide, fini) appelé vocabulaire de sortie. Les éléments sont des actions sur les variables considérées (affectation, incrémentation, etc).

- Une fonction f dite fonction de transition : f : E X S  $\rightarrow$  S